1.中断:一种使CPU中止正在执行的程序而转去处理特殊事件的操作。

2.中断源:引起中断的事件。

(1)内部中断源,由程序中安排的中断指令INT产生的中断,或由CPU的某些错误操作结果产生的中断。

① 溢出中断指令 INTO

② 中断指令INT N产生的中断

③ CPU错误引起的中断

④ 为debug设置的中断:单步中断,断点中断

(2)外部中断源

由外部设备随机引起的一般由中断控制器控制的中断或某些处理器(8087/80287)引起的中断。

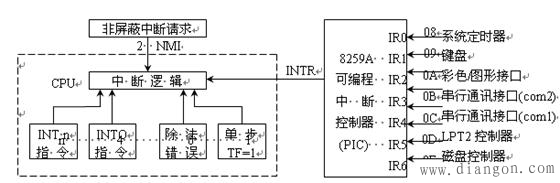

二、80x86 CPU的中断源.

如下图所示。

三、8086的中断分类

1.软件中断(内中断)

1)中断指令INT引起的中断:CPU执行完一条INT n (n不能为0、1、2、4的类型号)指令后,会立即产生中断,并且调用系统中相应的中断处理程序来完成中断功能。

2)处理CPU某些错误的中断(为处理运算结果的错误而设置)

3)除法错中断:中断类型为0。又称为除数为0中断。

4)溢出中断:中断类型为4。用INTO指令来中断发生溢出的算术操作,并把控制交给操作系统(此时要求OF=1并执行INTO指令)。如果未发生溢出,此时OF=0,则INTO不会引起中断,继续执行下面的一条指令。

5)为调试程序(DEBUG)设置的中断

单步中断:当标志位TF置为1时,每条指令执行后,CPU自动产生类型1的中断――单步中断。

断点中断:中断类型为3。通常调试程序时,把程序按功能分成几段,然后每段设一个断点。当CPU执行到断点时便产生中断,这时程序员可以检查各寄存器及有关存储单元的内容。

软终端过程

2.硬件中断(外中断):外中断来自处理机的随机发生的外部条件。

外中断源:有非屏蔽中断(NMI脚)和可屏蔽中断(INTR脚)两大类。

外中断与CPU的连接

非屏蔽中断接至8086/8088 CPU的NMI脚(17脚)。

可屏蔽中断通过8259A可编程中断控制器接至8086/8088 CPU的INTR脚(18脚)。

3.CPU响应可屏蔽外中断(INTR)的条件

IF=1才响应INTR请求的中断。

INTR未被8259A的中断屏蔽寄存器(IMR)屏蔽。

IMR的I/O端口地址为21H。其8位对应8个外设的中断请求。

某位为0允许该外设中断,某位为1则禁止该外设中断。

4.CPU响应非屏蔽外中断(NMI)是无条件的。该中断类型号为2。

8259A的中断结束命令EOI及中断命令寄存器(OCW2)

8259A的中断命令寄存器的端口地址为20H。其内容为:

中断结束命令EOI是使8259A的中断命令寄存器的第5位(EOI位)置1,清除当前中断服务寄存器ISR中对应的ISn位,以告诉8259A该中断已结束。

四、中断向量表

1.中断类型号:每个中断都被安排一个以示区别的8位的类型编号称为中断类型号。80x86中断系统能处理256种类型的中断,类型号为0~0FFH。

2.中断向量表:各个中断类型的处理子程序的入口地址表。存放于00000~003FFH的1KB单元中。低两位字节存放中断处理程序的偏移地址,高两位存放段地址。每个类型的中断向量地址占用4个字节的存储单元。

3.内部中断的操作步骤

(1)取中断类型号;

(2)计算中断向量地址;

(3)取中断向量:偏移地址→(IP),段地址→(CS);

(4)转入执行中断处理程序;

(5)中断返回到INT指令的下一条指令。

4.设置中断向量:在检查或设置任何中断向量时,总是避免直接使用中断向量的绝对地址,而是使用DOS系统功能调用(21H)存取中断向量。

1)设置中断向量:把由AL指定的中断类型的中断向量DS:DX放置到中断向量表中。

预置:AH=25H

AL=中断类型号

DS:DX=中断向量

执行:INT 21H

2)取中断向量:把由AL指定的中断类型的中断向量从中断向量表中取到ES:BX中。

预置:AH=35H

AL=中断类型号

执行:INT 21H ;中断向量作为出口信息已在ES:BX中

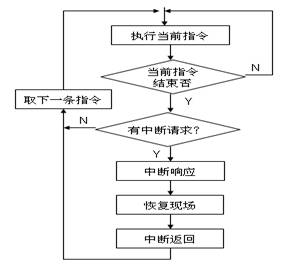

5.中断过程:当中断发生时,由中断机构自动完成下列动作:

(1)取中断类型号N

(2)标志寄存器(FLAGS)内容入栈

(3)当前代码段寄存器(CS)内容入栈

(4)当前指令计数器(IP)内容入栈

(5)禁止外部中断和单步中断( IF=0,TF=0 )

(6)从中断向量表中取(4×N)中的字节内容送IP,取(4×N+2)中的字节内容送CS

(7)转中断处理程序。中断处理程序需注意:

1)如在执行中断处理程序中还允许中断,可用STI置IF=1来开中断;

2)注意保护现场和恢复现场;

3)中断处理程序返回时使用IRET指令。

6.中断优先级和中断嵌套

2)IBM PC的可屏蔽中断(INTR)的优先级由高到低为:IR0,IR1,IR2,IR3,IR4,IR5,IR6,IR7。但是可以由8259A的中断命令寄存器(OCW2)的最高两位D7、D6位

3)置为循环的优先级。

4)中断嵌套:正在运行的中断处理程序又被中断称为中断嵌套。

一般是高级中断嵌套低级中断,此时要求低级中断的处理程序中要有开中断指令STI。被同级或低级中断源嵌套,除了使IF=1外,还要求向8259A发中断结束命令EOI。

7.中断处理程序

1)中断准备:在主程序中设置。

设置中断向量

设置设备的中断屏蔽位

设置CPU的中断允许位IF (开中断)

2)中断响应:由硬件自动完成。

外设接口送中断请求给CPU

当前指令执行完后,CPU送中断响应信号给外设接口

CPU接收中断类型号

当前的FLAGS,CS和IP保存入栈

清除TF和IF

中断向量送IP和CS

3)中断处理程序的编写方法与标准子程序类似,编写步骤如下:

保护现场,即保存寄存器内容

如允许中断嵌套,则开中断(STI) 使IF=1

处理中断内容

关中断

送中断结束命令(EOI)给8259A的中断命令寄存器(OCW2)以清除8259A的ISR中对应的ISn位

恢复现场,即恢复寄存器的内容

返回被中断的程序(IRET,中断返回)

全站搜索