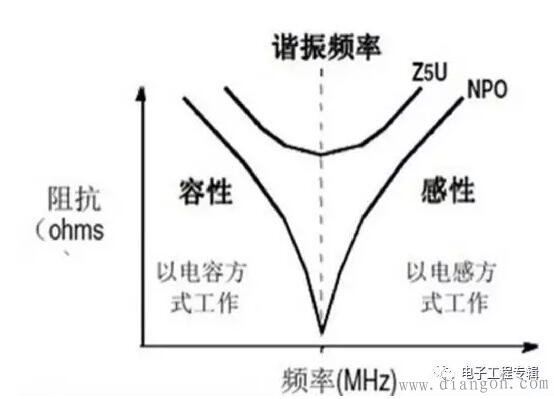

电容的容值选择一般取决于电容的谐振频率。

不同封装的电容有不同的谐振频率,下表列出了不同容值不同封装的电容的谐振频率:

需要注意的是数字电路的去耦,低的ESR值比谐振频率更为重要,因为低的ESR值可以提供更低阻抗的到地通路,这样当超过谐振频率的电容呈现感性时仍能提供足够的去耦能力。

降低去耦电容ESL的方法:

去耦电容的ESL是由于内部流动的电流引起的,使用多个去耦电容并联的方式可以降低电容的ESL影响,而且将两个去耦电容以相反走向放置在一起,从而使它们的内部电流引起的磁通量相互抵消,能进一步降低ESL。(此方法适用于任何数目的去耦电容,注意不要侵犯DELL公司的专利)

IC去耦电容的数目选择

在设计原理图的时候,经常遇到的问题是为芯片的电源引脚设计去耦电容,上面已经介绍了去耦电容的容值选择,但是数目选择怎么确定呢?理论上是每个电源引脚最好分配一个去耦电容,但是在实际情况中,却经常看到去耦电容的数目要少于电源引脚数目的情况,如freescale提供的iMX233的PDK原理图中,内存SDRAM有15个电源引脚,但是去耦电容的数目是10个。

去耦电容数目选择依据:

在布局空间允许的情况下,最好做到一个电源引脚分配一个去耦电容,但是在空间不足的时候,可以适当削减电容的数目,具体情况应该根据芯片上电源引脚的具体分布决定,因为厂家在设计IC的时候,经常是几个电源引脚在一起,这样可以共用去耦电容,减少去耦电容的数目。

全站搜索