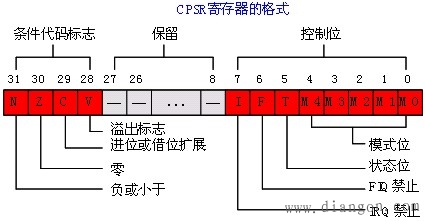

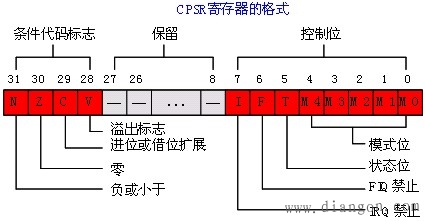

ARM7TDMI内核包含1个CPSR和5个供异常处理程序使用的SPSR。CPSR反映了当前处理器的状态,其包含:

(1)4个条件代码标志(负(N)、零(Z)、进位(C)和溢出(V) );

(2)2个中断禁止位,分别控制一种类型的中断;

(3)5个对当前处理器模式进行编码的位;

(4)1个用于指示当前执行指令(ARM还是Thumb)的位。

每个异常模式还带有一个程序状态保存寄存器 (SPSR),它用于保存在异常发生之前的CPSR。CPSR和SPSR通过特殊指令进行访问。详细信息请参阅第4章 。

关于“条件代码标志”:大多数“数值处理指令”可以选择是否影响条件代码标志位。通常如果指令带S后缀,则该指令的执行会影响条件代码标志;但有一些指令的执行总是会影响条件代码标志。

N、Z、C和V位都是条件代码标志。通过算术操作、逻辑操作、MSR或者LDM指令可以对这些位进行设置。所有ARM指令都可按条件来执行,而Thumb指令中只有分支指令可按条件执行。

各标志位的含义如下:

(1)N 运算结果的最高位反映在该标志位。对于有符号二进制补码,结果为负数时N=1,结果为正数或零时N=0;

(2)Z 指令结果为0时Z=1(通常表示比较结果“相等”),否则Z=0;

(3)C 当进行加法运算(包括CMN指令),并且最高位产生进位时C=1,否则C=0。当进行减法运算(包括CMP 指令),并且最高位产生借位时C=0,否则C=1。对于结合移位操作的非加法/减法指令,C为从最高位最后移出的值,其它指令C通常不变;

(4)V当进行加法/减法运算,并且发生有符号溢出时V=1,否则V=0,其它指令V通常不变。

关于“控制位”:CPSR的最低8位为控制位,当发生异常时,这些位被硬件改变。当处理器处于一个特权模式时,可用软件操作这些位。它们分别是:中断禁止位;T位;模式位。

关于“中断禁止位”包括I和F位:

(1)当I位置位时,IRQ中断被禁止;

(2)当F位置位时,FIQ中断被禁止。

关于“T位”反映了正在操作的状态:

(1)当T位置位时,处理器正在Thumb状态下运行;

(2)当T位清零时,处理器正在ARM状态下运行。

关于“模式位”包括:M4、M3、M2、M1和M0,这些位决定处理器的操作模式。

注意:不是所有模式位的组合都定义了有效的处理器模式,如果使用了错误的设置,将引起一个无法恢复的错误。

对于“保留位”CPSR中的保留位被保留将来使用。为了提高程序的可移植性,当改变CPSR标志和控制位时,请不要改变这些保留位。另外,请确保您程序的运行不受保留位的值影响,因为将来的处理器可能会将这些位设置为1或者0。

-

标签: