系统控制模块概述

系统控制模块包括一些系统构件和控制寄存器,它们具有众多与芯片内其它外设无关的功能。系统控制模块包括:系统时钟单元、复位、外部中断输入、存储器映射控制、功率控制和唤醒定时器。

系统时钟

系统时钟概述

CPU正常工作需要有合适的时钟信号,包括ARM7内核使用的CCLK时钟,和芯片外设使用的PCLK时钟。

通过LPC2000系列微控制器的时钟产生单元产生ARM7内核和芯片外设正常工作所需要的时钟节拍。

晶体振荡器

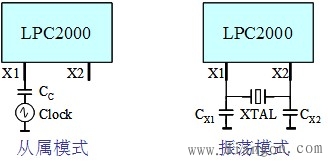

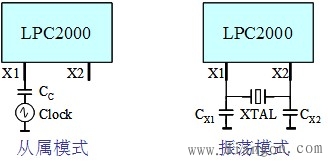

LPC2000微控制器可以使用内部的晶体振荡器产生时钟信号,也可以从外部引入时钟信号。

使用从属模式时,时钟信号通过X1引脚从外部输入,输入频率范围:1~50(MHz),其幅度不小于200m Vrms。

使用振荡模式时,时钟信号由内部晶体振荡器和外部连接的晶体振荡产生,振荡频率范围:1~30(MHz)。

注意:如果使用了ISP下载功能或者连接PLL提高频率,则输入的时钟频率范围必须在10~25(MHz)之间。

锁相环(PLL)

由晶体振荡器输出的时钟信号,通过PLL升频,可以获得更高的系统时钟(CCLK)。

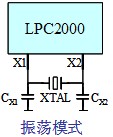

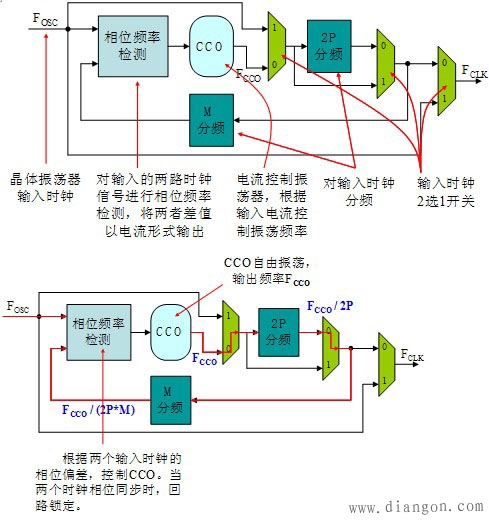

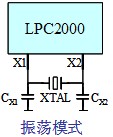

PLL接受的输入时钟频率范围为10~25MHz,通过一个电流控制振荡器(CCO)倍增到10~60MHz。

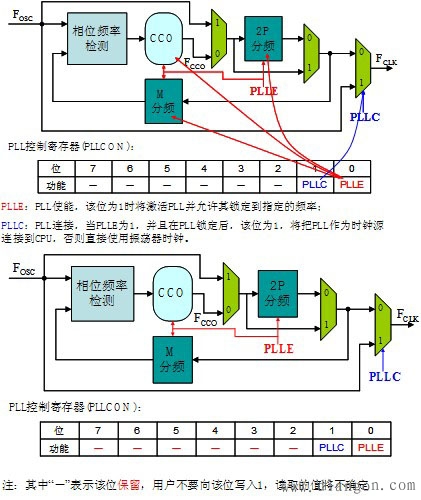

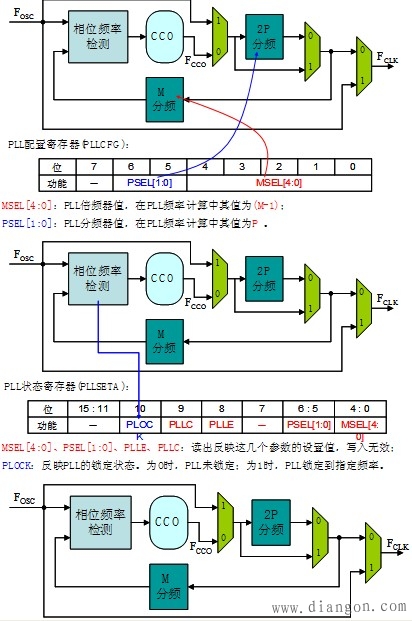

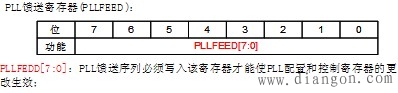

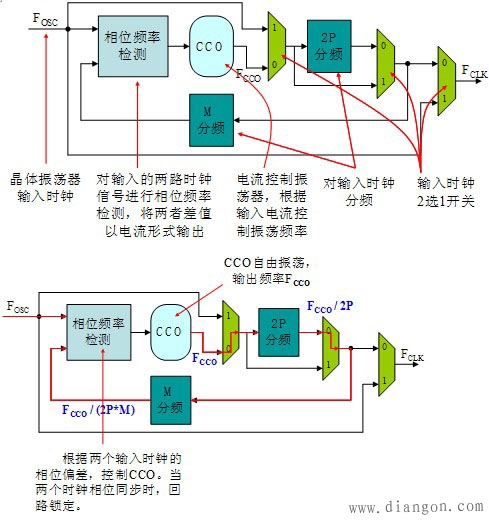

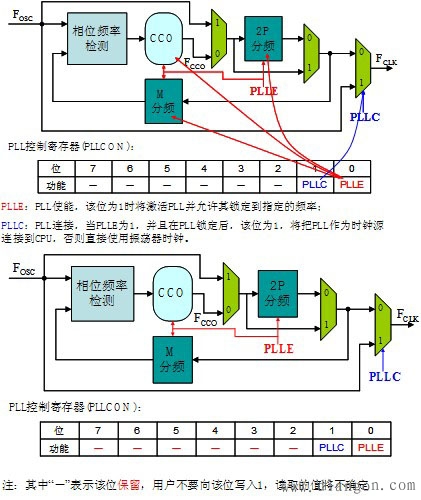

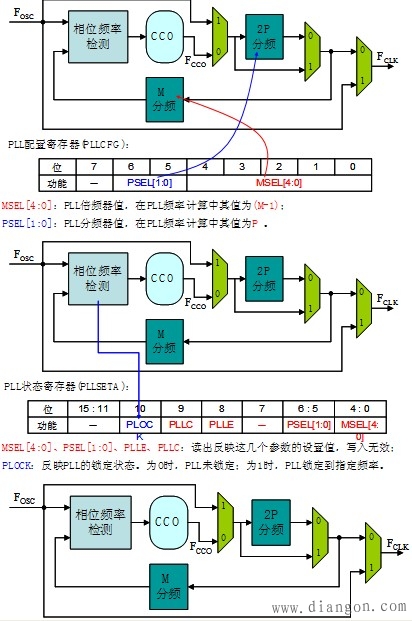

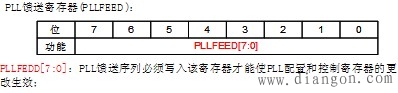

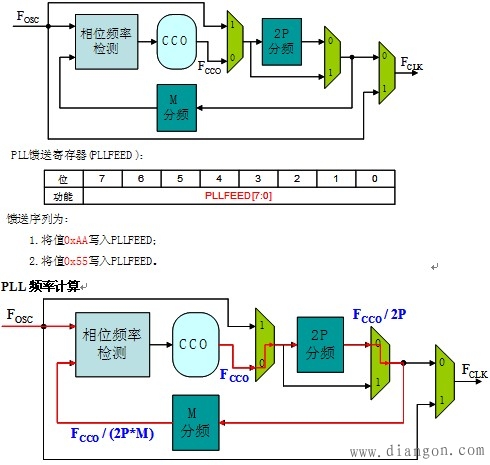

PLL内部结构

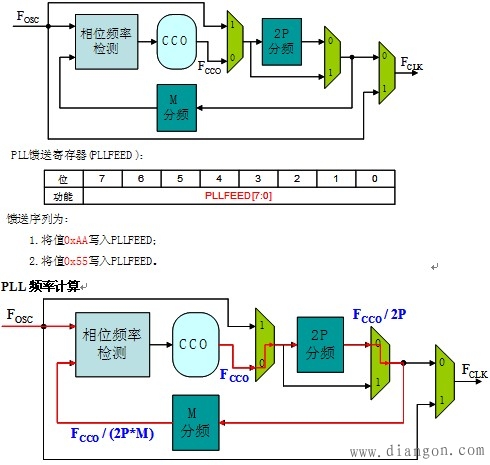

PLL相关寄存器

回路锁定后:FOSC = FCCO / (2P × M)

FCLK = FOSC × M

FOSC:晶振频率; FCCO :CCO振荡器输出频率FCCLK:处理器时钟频率; M:PLL倍频值 P:PLL分频值

必须满足的条件:

FOSC范围:10MHz~25MHz; FCCLK范围:10MHz~60MHz; FCCO范围:156MHz~320MHz;

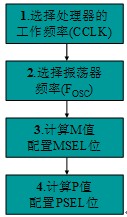

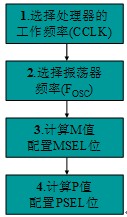

锁相环(PLL)计算流程

(1)、根据处理器的整体要求、UART波特率的支持等因素来决定。外围器件的时钟频率可以低于处理器频率

(2)、CCLK 必须为FOSC的整数倍。

(3)、M = CCLK / FOSC,取值范围1~32。写入MSEL的值为(M-1)。

(4)、选择合适的P值,使FCCO在限制范围内。P只能取1、2、4或8。写入PSEL的值为P。

锁相环(PLL)计算实例

系统要求:FOSC=10MHz、CCLK= 60MHz

1.计算M值:M= CCLK / FOSC =6 ;

2.设置MSEL位:写入值为(M-1)=5;

3. 设置PSEL位:P=FCCO/(CCLK×2)

=(156~320)/120=1.3~2.67

所以P取整数2,PSEL写入值为2。

锁相环(PLL)注意要点

(1)PLL在芯片复位或进入掉电模式时被关闭并旁路,在掉电唤醒后不会自动恢复PLL的设定;

(2)PLL只能通过软件使能;

(3)PLL在激活后必须等待其锁定,然后才能连接;

(4)PLL如果设置不当将会导致芯片的错误操作。

VPB分频器

VPB分频器将PLL输出的时钟信号分频后作为芯片外设的时钟。